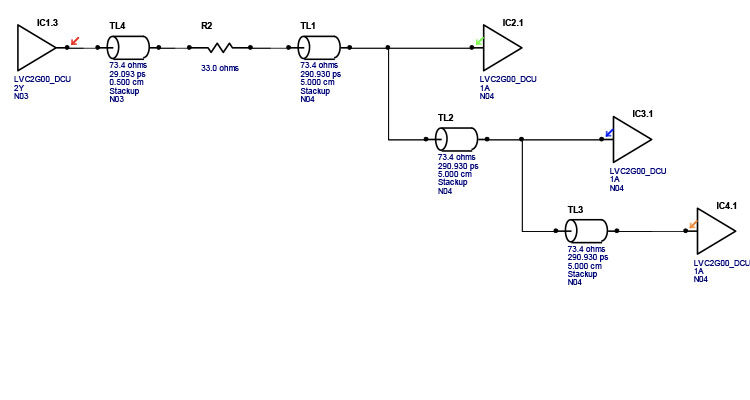

今回は1対多のBUS信号などを一筆書き配線している信号について、レシーバ3つを配線した場合の波形がどのように変化するかシミュレーションで確認してみました。

このような配線時は終端抵抗が一般的かと思いますが、ドライブ側とレシーバ側にダンピング抵抗を入れた場合どのような波形になるか見てみたいと思います。レシーバが多くぶら下がっている信号は波形が乱れます。メモリ関係の配線などにも見られます。負荷は同じもので確認しています。

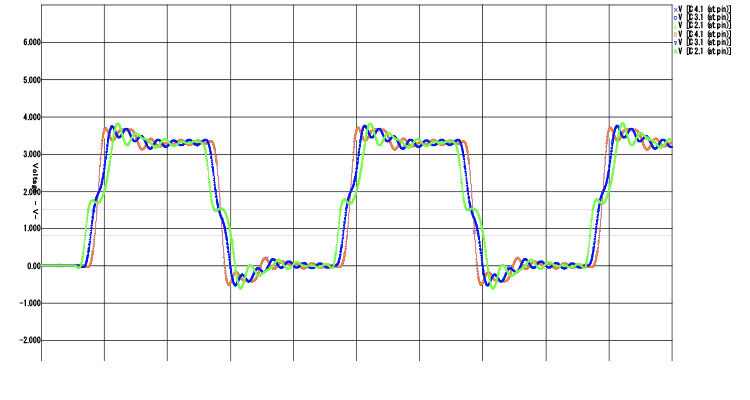

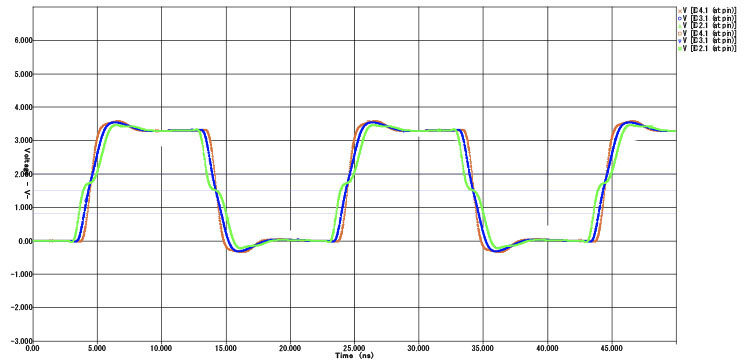

波形を見て見ると、リンギングが出ており、反射の影響か、IC2側のエッジに段付きが発生しております。

配線の途中にあるICのため、反射の影響を受けやすくなっていると考えられます。

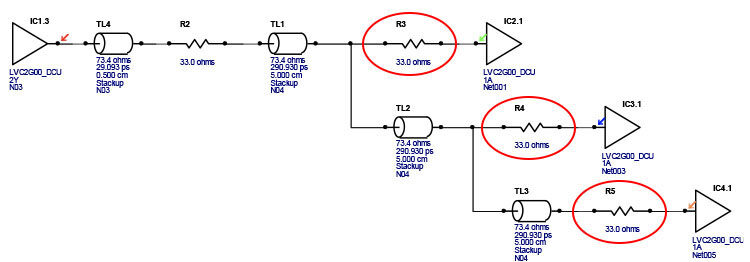

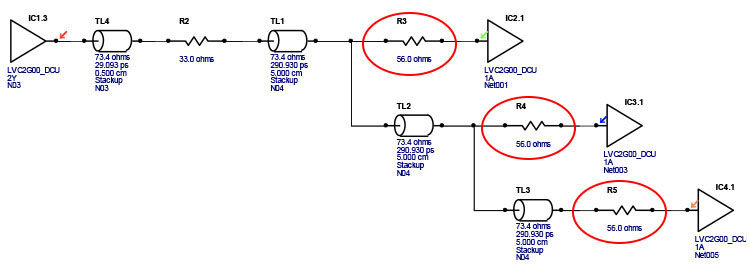

●各レシーバの前にダンピング抵抗33Ωをそれぞれ追加して、波形が良くなるか確認してみます。

ダンピング抵抗を追加することにより、リンギングが小さくなり、波形が少しきれいになりましたが、IC2側のエッジの段付きは改善されませんでした。

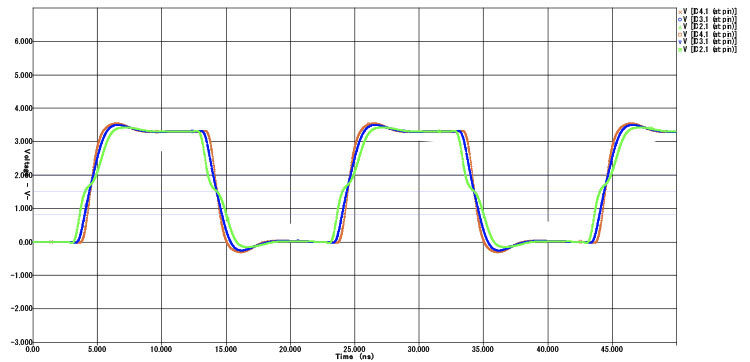

●各レシーバの前のダンピング抵抗を試しに56Ωにして、波形を確認してみました。

ダンピング抵抗の値を少し大きくしてみましたが、効果はほとんどありませんでした。

一筆書き配線でレシーバ3つの時の波形を確認してみましたが、配線の途中にあるICが反射の影響を受けやすくなるので波形が良くありませんでした。

ダンピング抵抗をレシーバ側にも取り付けた場合、リンギングを小さくする効果や波形を少しだけきれいにする効果があるようですが、IC2側の段付きをとることができませんでした。

このような配線の時は、終端抵抗が一般的かと思いますが、レシーバが3つの場合や高速信号の場合はシミュレーションをして進め方を決めておくことがおすすめです。